# **Video Starter Kit**

# **User Guide**

UG217 (v1.5) October 26, 2006

Xilinx is disclosing this Document and Intellectual Property (hereinafter "the Design") to you for use in the development of designs to operate on, or interface with Xilinx FPGAs. Except as stated herein, none of the Design may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Any unauthorized use of the Design may violate copyright laws, trademark laws, the laws of privacy and publicity, and communications regulations and statutes.

Xilinx does not assume any liability arising out of the application or use of the Design; nor does Xilinx convey any license under its patents, copyrights, or any rights of others. You are responsible for obtaining any rights you may require for your use or implementation of the Design. Xilinx reserves the right to make changes, at any time, to the Design as deemed desirable in the sole discretion of Xilinx. Xilinx assumes no obligation to correct any errors contained herein or to advise you of any correction if such be made. Xilinx will not assume any liability for the accuracy or correctness of any engineering or technical support or assistance provided to you in connection with the Design.

THE DESIGN IS PROVIDED "AS IS" WITH ALL FAULTS, AND THE ENTIRE RISK AS TO ITS FUNCTION AND IMPLEMENTATION IS WITH YOU. YOU ACKNOWLEDGE AND AGREE THAT YOU HAVE NOT RELIED ON ANY ORAL OR WRITTEN INFORMATION OR ADVICE, WHETHER GIVEN BY XILINX, OR ITS AGENTS OR EMPLOYEES. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DESIGN, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND NONINFRINGEMENT OF THIRD-PARTY RIGHTS.

IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOST DATA AND LOST PROFITS, ARISING FROM OR RELATING TO YOUR USE OF THE DESIGN, EVEN IF YOU HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. THE TOTAL CUMULATIVE LIABILITY OF XILINX IN CONNECTION WITH YOUR USE OF THE DESIGN, WHETHER IN CONTRACT OR TORT OR OTHERWISE, WILL IN NO EVENT EXCEED THE AMOUNT OF FEES PAID BY YOU TO XILINX HEREUNDER FOR USE OF THE DESIGN. YOU ACKNOWLEDGE THAT THE FEES, IF ANY, REFLECT THE ALLOCATION OF RISK SET FORTH IN THIS AGREEMENT AND THAT XILINX WOULD NOT MAKE AVAILABLE THE DESIGN TO YOU WITHOUT THESE LIMITATIONS OF LIABILITY.

The Design is not designed or intended for use in the development of on-line control equipment in hazardous environments requiring failsafe controls, such as in the operation of nuclear facilities, aircraft navigation or communications systems, air traffic control, life support, or weapons systems ("High-Risk Applications"). Xilinx specifically disclaims any express or implied warranties of fitness for such High-Risk Applications. You represent that use of the Design in such High-Risk Applications is fully at your risk.

© 2005, 2006 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

# **Revision History**

## Video Starter Kit UG217 (v1.5) October 26, 2006

The following table shows the revision history for this document.

| Date     | Version | Revision                                                                                                                   |  |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------|--|

| 12/22/05 | 1.0     | itial Xilinx release.                                                                                                      |  |

| 02/13/06 | 1.1     | Edits throughout the document.                                                                                             |  |

| 03/14/06 | 1.2     | Minor edits in Chapter 6. Replaced Figure 6-5.                                                                             |  |

| 06/27/06 | 1.3     | Minor edits.                                                                                                               |  |

| 10/10/06 | 1.4     | Edits and additions to Chapter 5, "VSK Diagnostics and Support Tool Kit" and Chapter 7, "Compiling the VIODC FPGA Design." |  |

| 10/26/06 | 1.5     | Updated Figure 5-6 and Figure 5-9. Added new Table 5-5.                                                                    |  |

# **Contents**

| Preface: About This Guide                         |    |

|---------------------------------------------------|----|

| Guide Contents                                    | 13 |

| Additional Resources                              |    |

| Conventions                                       |    |

| Typographical                                     |    |

| Online Document                                   |    |

| Offinic Document                                  | 10 |

| Chapter 1: Video Starter Kit Overview             |    |

| Key Features                                      | 17 |

| VSK Hardware Overview                             | 18 |

| ML402 Development Platform                        |    |

| XC4VSX35 FPGA                                     |    |

| Gigabit Ethernet                                  | 18 |

| RS-232 Port                                       | 19 |

| DDR Memory                                        |    |

| System Ace Controller                             |    |

| I/O Expansion Header                              |    |

| Video Input and Output Daughter Card              |    |

| LVDS Camera Input                                 |    |

| Component Video I/O                               |    |

| DVI Digital Video I/O                             |    |

| S-Video and Composite Video                       |    |

| XCV2P7 FPGA                                       |    |

|                                                   |    |

| VSK Demo Application                              |    |

| Software and Application Updates Available Online |    |

| Software Support Package Overview                 |    |

| Software Simulation                               |    |

| Hardware Implementation                           |    |

| Hardware Co-Simulation                            |    |

| VIODC HDL Support Package                         |    |

| System Generator Support                          |    |

| DDR Memory Controller                             |    |

| Pcore Export and EDK Import                       |    |

| Multiple Subsystem Generator                      |    |

| Ethernet Co-Sim                                   |    |

| Diagnostics                                       |    |

| Demonstrations                                    |    |

| MPEG Decoding Demo.                               |    |

| VSK Diagnostics Camera Demo                       |    |

| SDI Demo                                          |    |

| Video Demo in Verilog                             | ∠6 |

# **Chapter 2: Developing Video Applications In System Generator**

| Overview                                                | 27          |

|---------------------------------------------------------|-------------|

| Real-Time Operation                                     | 27          |

| Hardware-in-the-Loop Video Simulation                   | 28          |

| Hardware-in the Loop Co-Simulation                      |             |

| Software Simulation Modes                               |             |

| Hardware-Software Systems                               |             |

| Generating a Video Processor as an EDK Pcore            |             |

| Hardware-Software Communication.                        |             |

| Memory Mapped Hardware                                  |             |

| MicroBlaze Processor Communicating with a Shared Memory |             |

| Hardware-Software Co-Simulation                         | 32          |

| EDK Co-Simulation                                       |             |

| VSK Video Processor Development System                  |             |

| ML402 FPGA                                              |             |

| MicroBlaze Subsystem                                    |             |

| VIODC FPGA                                              |             |

|                                                         |             |

| Chapter 3: EDK Integration                              |             |

| · · ·                                                   | 0.5         |

| Overview                                                |             |

| MicroBlaze Processor Interface                          |             |

| EDK Pcore Export Mode                                   |             |

| EDK Import Mode                                         |             |

| Adding a Processor to a System Generator Design         |             |

| The EDK Processor Block                                 | 36          |

| Interfacing the EDK Processor to User Logic             |             |

| Exporting the Design as a Pcore                         |             |

| Importing an EDK Project into System Generator          |             |

| Writing Software Code                                   | 41          |

|                                                         |             |

| Chapter 4: Hardware Co-Simulation                       |             |

| Hardware Co-Simulation Overview                         | 45          |

| Co-Simulation Communication Primitives                  | <b> 4</b> 5 |

| Ports                                                   |             |

| Shared Register                                         |             |

| Shared Memory                                           | 46          |

| FIFO                                                    | 47          |

| Pad                                                     |             |

| Shared Memory Read/Write Blocks                         | 49          |

| Co-Simulation Interfaces                                | 50          |

| JTAG                                                    |             |

| PCI                                                     |             |

| Network-Based Ethernet Co-Simulation                    |             |

| Point to Point Ethernet Co-Simulation                   |             |

| Third Party Co-Simulation                               |             |

| Building a Co-Sim Project                               |             |

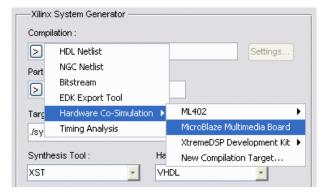

| Choosing a Compilation Target                           | 52          |

| Invoking the Code Generator                      | 5 | 2  |

|--------------------------------------------------|---|----|

| Hardware Co-Simulation Blocks                    | 5 | 4  |

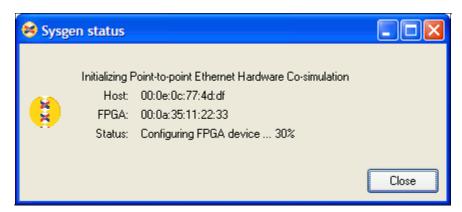

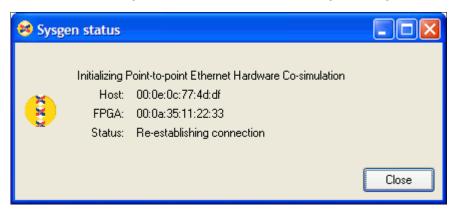

| Ethernet Co-Sim Setup                            | 5 | 5  |

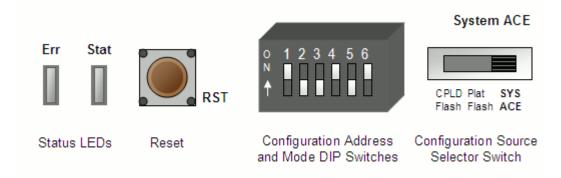

| System ACE Setup                                 | 5 | 6  |

| Prepare the System ACE Compact Flash Card        | 5 | 6  |

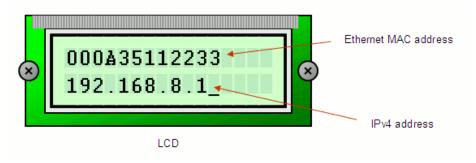

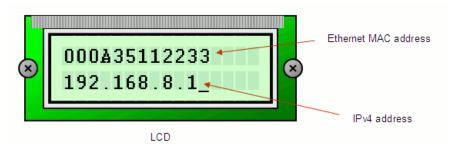

| Assign an Ethernet MAC Address and IPv4 Address  |   |    |

| Adjust On-Board Settings for System ACE          |   |    |

| System ACE Troubleshooting                       |   |    |

| Verify System ACE Settings                       |   |    |

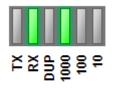

| Verify Ethernet Interface And Connection Status  |   |    |

| Ensuring a Correct Setup                         |   |    |

| Choose the Configuration Method                  |   |    |

| Configure the Ethernet Interface Settings        |   |    |

| Co-Simulating the Design                         |   |    |

| Frame Based Co-Simulation Tutorial               |   |    |

| Traine based Co-Sintulation rutorial             | 0 | '4 |

| Chapter 5: VSK Diagnostics and Support Tool Kit  |   | =  |

|                                                  |   |    |

| VIODC Design.                                    |   |    |

| IIC Interface                                    |   |    |

| VIODC-ML402 Serial Port                          |   |    |

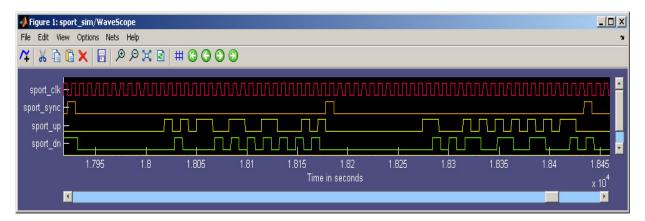

| VIODC Serial Port Interface                      |   |    |

| VIODC Registers                                  |   |    |

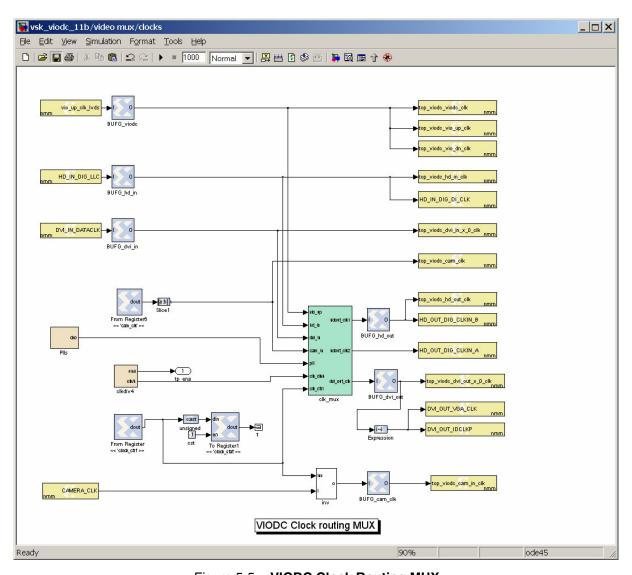

| Clock Routing                                    | 7 | ′3 |

| VIO Design                                       | 7 | '3 |

| VIO Mask                                         |   |    |

| Compile Type                                     |   |    |

| Input Type                                       |   |    |

| Output Type                                      |   |    |

| Mask Modifications                               |   |    |

| EDK Pcore                                        |   |    |

|                                                  |   |    |

| Bitstream                                        |   |    |

| VIO I/O Buses                                    |   |    |

| VIO Registers                                    |   |    |

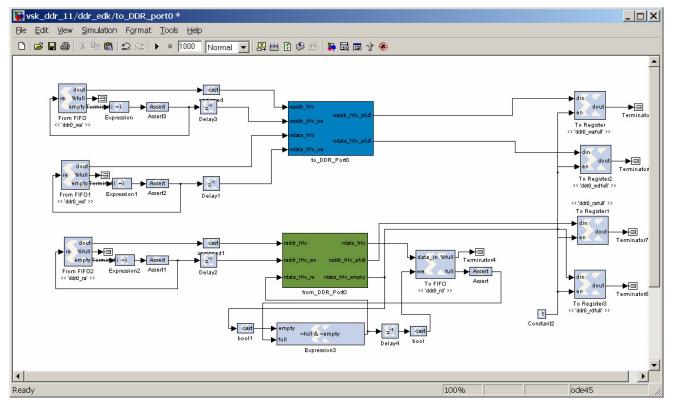

| DDR Design                                       | 8 | 0  |

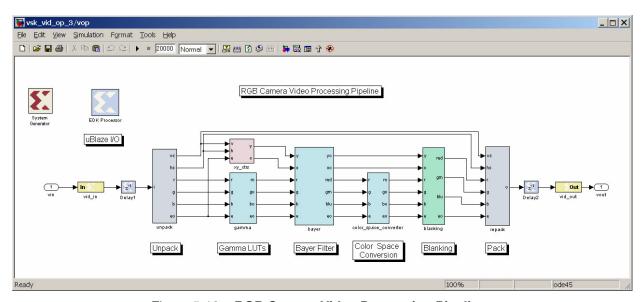

| VOP Design                                       | 8 | 31 |

| Running the Diagnostics                          |   |    |

| Hardware Setup                                   |   |    |

| Software Setup                                   |   |    |

| Configure the ML402 Board to Run the Diagnostics |   |    |

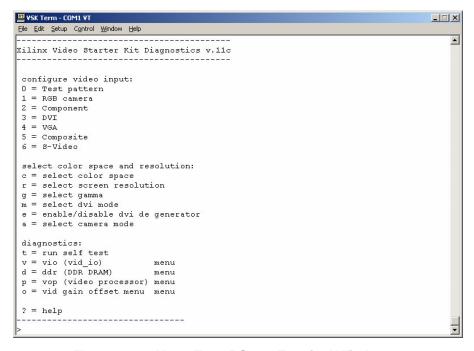

| Running the VSK Diagnostics                      |   |    |

| ŭ ŭ                                              |   |    |

| RGB Camera Test                                  |   |    |

| Component Video Input Test                       |   |    |

| DVI Input Test                                   |   |    |

| VGA Input Test                                   |   |    |

| Composite Input Test                             |   |    |

| S-Video Input Test                               |   |    |

| Additional Diagnostics and Controls              |   |    |

| VIO Diagnostics Peek and Poke Facility           |   |    |

| VIO Diagnostics - Device Configure Facility      |   |    |

| Troubleshooting                                  | 8 | 8  |

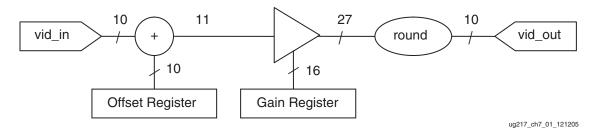

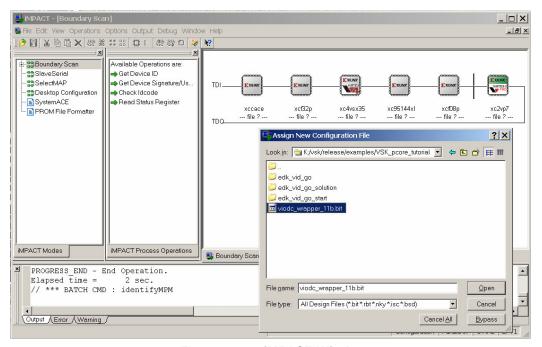

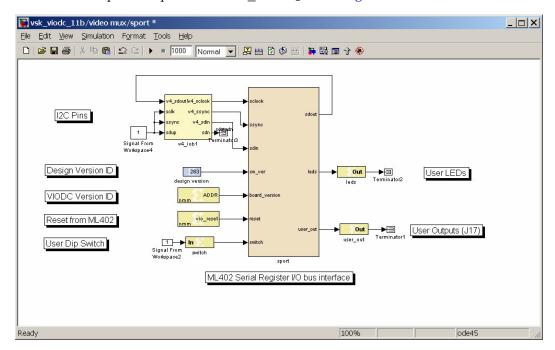

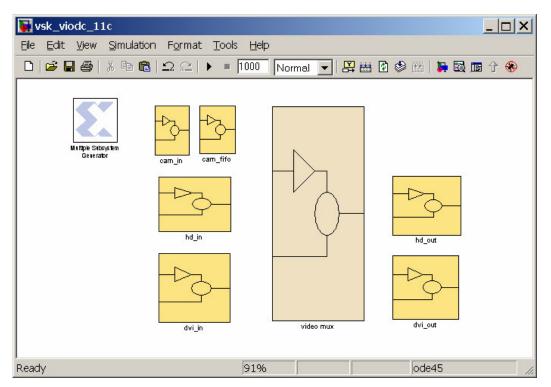

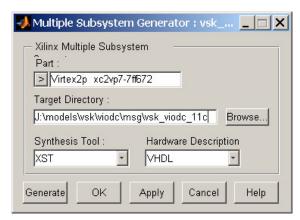

# Chapter 6: VSK Tutorial Gain and Offset Theory ...... 90 System Architecture 90 Video Stream Format......90 **Tutorial Files**.......91 Generating the Pcore .......95 Chapter 7: Compiling the VIODC FPGA Design Loading the VIODC Design to the XCV2P7 FPGA on the VIODC Board .... 105 **Appendix A: VSK I/O Connector Location Pictures**

# Schedule of Figures

| Chapter 1: Video Starter Kit Overview                                                                     |    |

|-----------------------------------------------------------------------------------------------------------|----|

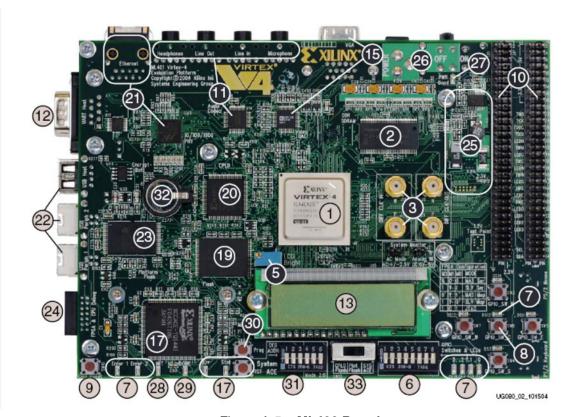

| Figure 1-1: ML402 Block Diagram                                                                           | 18 |

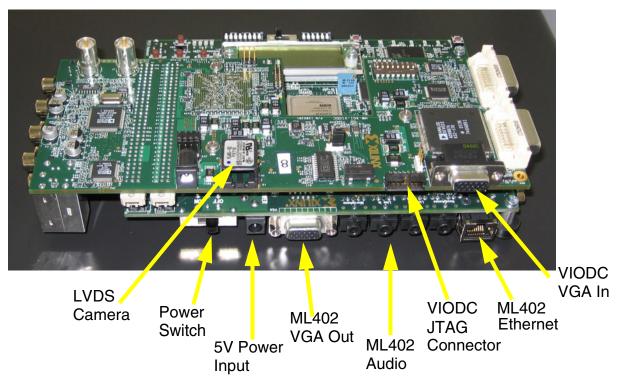

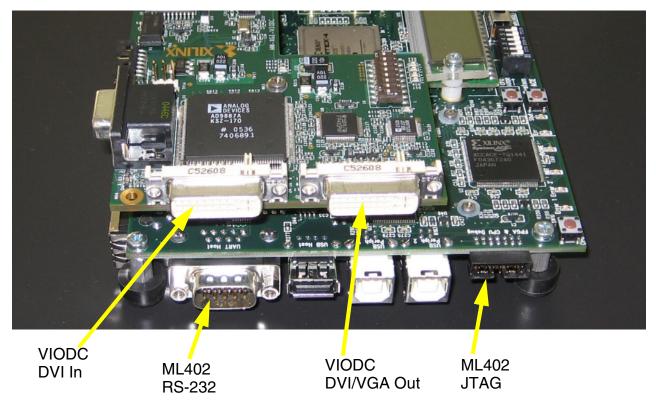

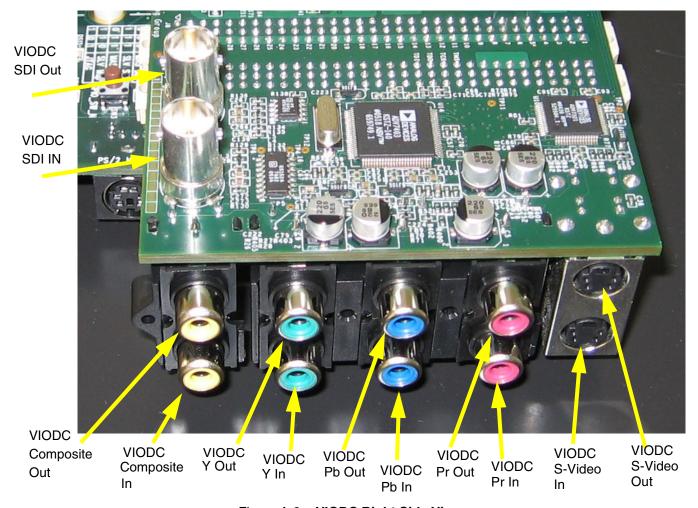

| Figure 1-2: VIODC and ML402 Board with Video Interface Ports Labeled                                      | 19 |

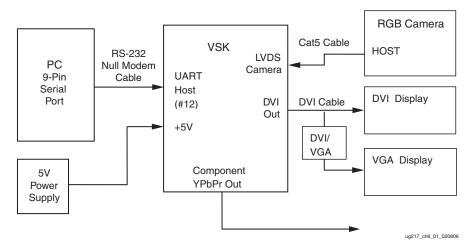

| Figure 1-3: RGB Camera Demo Setup                                                                         | 21 |

| Figure 1-4: RGB Camera Video Processing Pipeline                                                          |    |

| Figure 1-5: Block Diagram of VSK RGB Camera Demo Included in the VSK                                      | 22 |

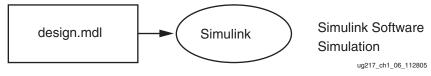

| Figure 1-6: Software Simulation Flow                                                                      |    |

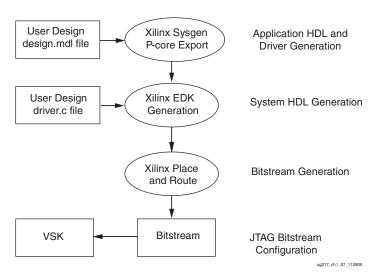

| Figure 1-7: Real-Time Deployment Flow                                                                     | 23 |

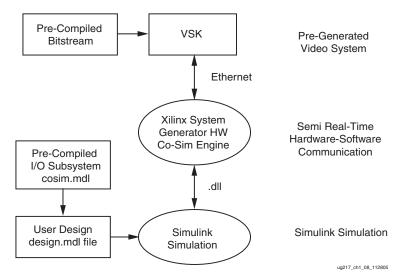

| Figure 1-8: Hardware-in-the-Loop Flow                                                                     | 24 |

| Chapter 2: Developing Video Applications                                                                  |    |

| In System Generator                                                                                       |    |

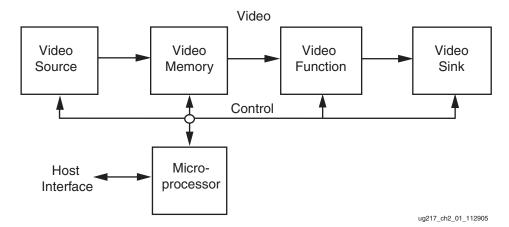

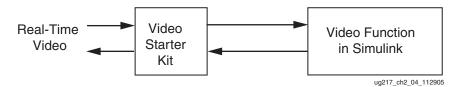

| Figure 2-1: Video System Diagram                                                                          | 27 |

| Figure 2-2: Real-Time Video Processing                                                                    | 28 |

| Figure 2-3: Hardware-in-the-Loop Video Processing                                                         | 28 |

| Figure 2-4: Simulink Diagram Implementing a Gain and Offset Function Using Xilinx System Generator Blocks | 29 |

| Figure 2-5: Gain and Offset Function Compiled to a Hardware Co-Sim Token .                                | 29 |

| Figure 2-6: Software Simulation Using Live Video Signals with Simulink                                    | 30 |

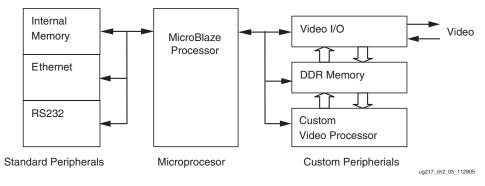

| Figure 2-7: MicroBlaze Processor with Peripherals and Three Custom Video Peripherals                      | 30 |

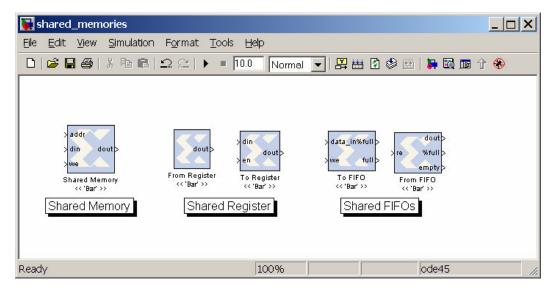

| Figure 2-8: System Generator Shared Memory Blocks                                                         |    |

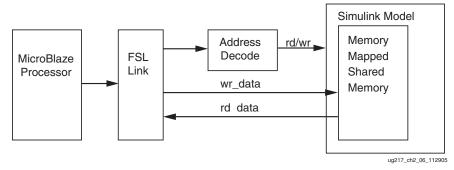

| Figure 2-9: MicroBlaze Processor Communicating with a Shared Memory                                       | 31 |

| Figure 2-10: EDK Import with Registered IO                                                                | 32 |

| Figure 2-11: ML402 FPGA                                                                                   | 33 |

| Chapter 3: EDK Integration                                                                                |    |

| Figure 3-1: Memory-Mapped User Logic                                                                      | 35 |

| Figure 3-2: EDK Processor Block                                                                           | 36 |

| Figure 3-3: EDK Processor GUI                                                                             | 37 |

| Figure 3-4: Export as a Pcore to EDK                                                                      | 38 |

| Figure 3-5: Launching Import Wizard                                                                       | 39 |

| Figure 3-6: EDK Import Wizard                                                                             | 39 |

| Figure 3-7: Hardware Co-Simulation Options                                                                | 40 |

| Figure 3-8: Software Tab                                                                                  | 40 |

| Figure 3-9: Xilinx Platform Studio - Assembly View                                                        |    |

| Figure 3-10: Memory Map Documentation                                                                     | 42 |

# Chapter 4: Hardware Co-Simulation Figure 4-10: Example of a Run-time Hardware Co-Simulation Block Figure 4-11: Port Interface of a Run-time Co-Simulation Block Matches the Chapter 5: VSK Diagnostics and Support Tool Kit Figure 5-2: VIODC – Top-Level Design with Seven Independent Clock Domains . . . . 66

Figure 5-13: VSK Demo Setup

82

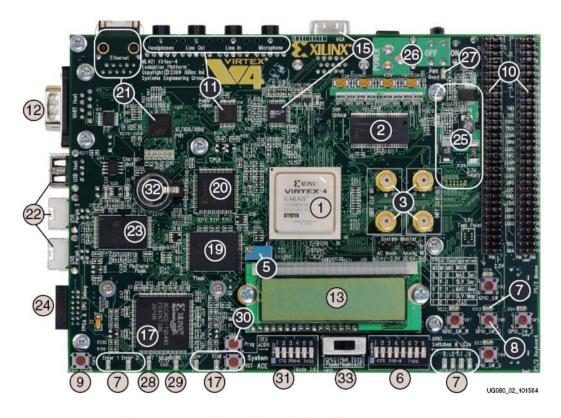

| I    | Eigure 5-14: ML402 Board - Top View                                               | 83  |

|------|-----------------------------------------------------------------------------------|-----|

| I    | Figure 5-15: Virtex-4 ML40x Evaluation Platform Components (Back)                 | 83  |

| I    | Figure 5-16: Configure the ML402 Board                                            | 84  |

| I    | Figure 5-17: HyperTerm RS-232 Terminal Window                                     | 85  |

| Chap | ter 6: VSK Tutorial                                                               |     |

| I    | Figure 6-1: Gain and Offset                                                       | 90  |

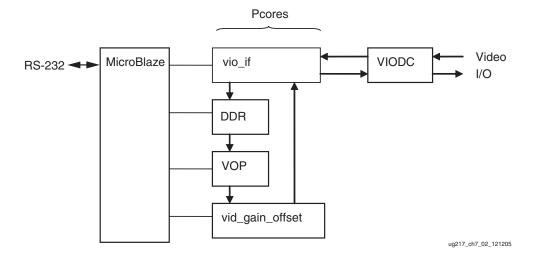

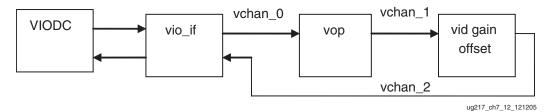

| I    | Figure 6-2: Gain and Offset System Architecture                                   | 90  |

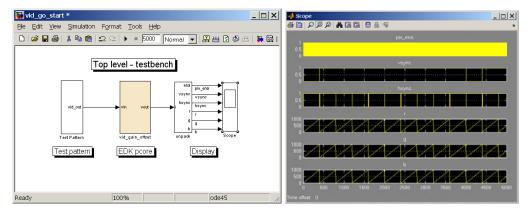

| I    | Figure 6-3: vid_go_start Simulation Results                                       | 92  |

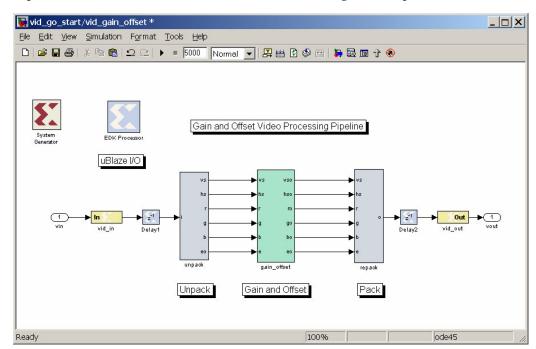

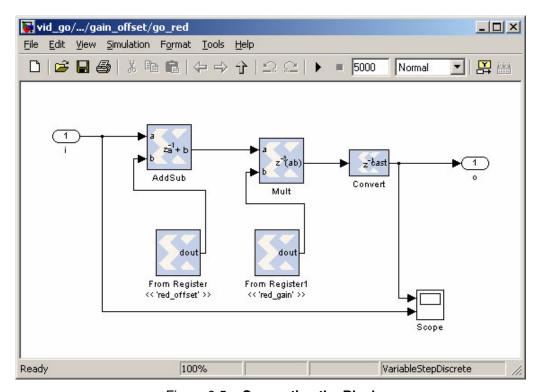

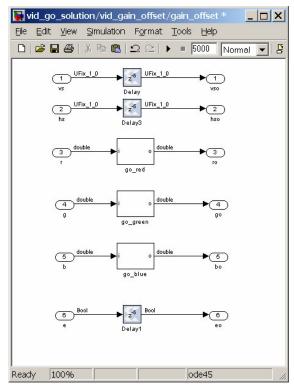

| I    | Figure 6-4: Gain and Offset Processing Pcore                                      | 92  |

| I    | <i>Eigure 6-5:</i> Connecting the Blocks                                          | 93  |

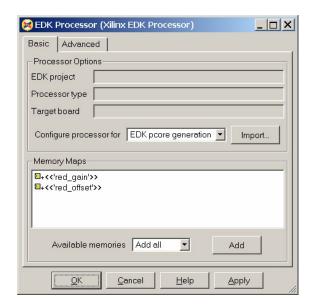

| I    | Figure 6-6: EDK Processor Configuration                                           | 94  |

| I    | Figure 6-7: Design Saved as vid_go.mdl                                            | 95  |

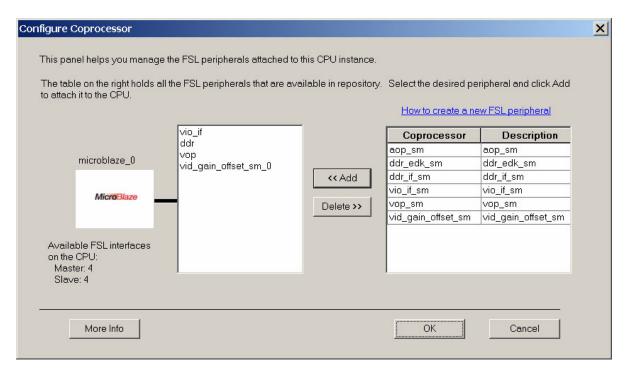

| I    | Figure 6-8: Generating the Pcore                                                  | 96  |

| I    | Figure 6-9: Configure Coprocessor Panel                                           | 97  |

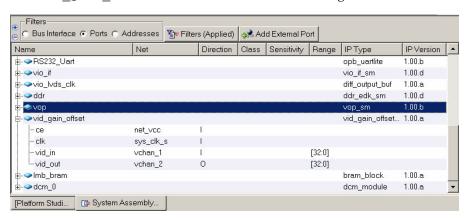

| I    | Figure 6-10: System Menu Showing New Imported Pcore                               | 97  |

| I    | Figure 6-11: Pcore Wiring with vid_gain_offset Pcore Inserted into Video Pipeline | 98  |

| I    | Figure 6-12: iMPACT Window                                                        | 00  |

| Chap | ter 7: Compiling the VIODC FPGA Design                                            |     |

| I    | Figure 7-1: VIODC Serial Register I/O Block                                       | .02 |

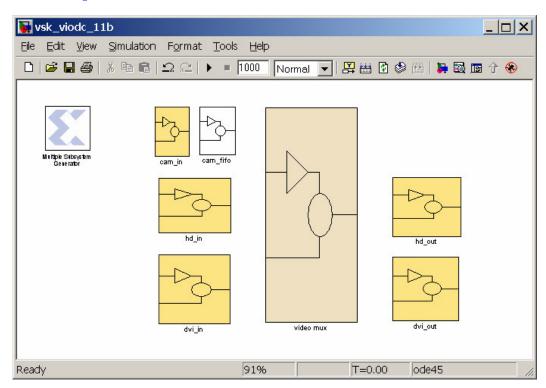

|      | Figure 7-2: vsk_viodc_xxx.mdl Top Level                                           |     |

| I    | Figure 7-3: MSG Generate Block                                                    | .03 |

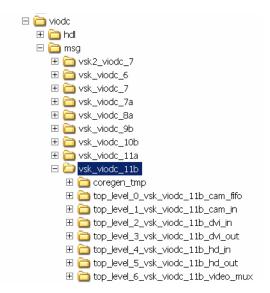

| I    | Figure 7-4: Directory Structure Generated by Multiple Subsystem Generator 1       | 04  |

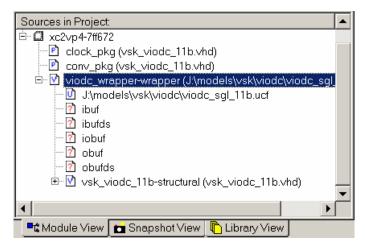

| I    | Figure 7-5: Project Navigator Source File View                                    | 05  |

| Appe | ndix A: VSK I/O Connector Location Pictures                                       |     |

| I    | Figure A-1: VIODC Rear View 1                                                     | .07 |

| I    | Figure A-2: VIODC Left Side View                                                  | .08 |

| I    | Figure A-3: VIODC Right Side View                                                 | .09 |

| I    | Figure A-4: LVDS Camera                                                           | 10  |

| I    | Figure A-5: ML402 Board                                                           | 11  |

| I    | Figure A-6: ML402 Evaluation Platform                                             | 12  |

# Schedule of Tables

| Chapter 1: | Video Starter Kit Overview                   |

|------------|----------------------------------------------|

| •          | Developing Video Applications<br>n Generator |

| Chapter 3: | EDK Integration                              |

| Table 3-1: | Pcore Directory Structure                    |

| Chapter 4: | Hardware Co-Simulation                       |

| Chapter 5: | VSK Diagnostics and Support Tool Kit         |

| Table 5-1: | VSK Support Toolkit Components               |

| Table 5-2: | VIODC Video Format                           |

| Table 5-3: | Available IIC Devices                        |

| Table 5-4: | VIODC Registers                              |

| Table 5-5: | VIO_IF GPIO Format                           |

| Table 5-6: | VIO Registers                                |

| Table 5-7: | Keystroke Menu                               |

| Table 5-8: | Available Devices                            |

| Chapter 6: | VSK Tutorial                                 |

| Chapter 7: | Compiling the VIODC FPGA Design              |

| Appendix A | : VSK I/O Connector Location Pictures        |

# About This Guide

This user guide provides a description of the Video Starter Kit (VSK) contents, features, hardware, and software. The Video Starter Kit hardware consists of a ML402 FPGA development platform with a Video Input and Output Daughter Card (VIODC) and an LVDS video camera. The Video Starter Kit can be used with System Generator to develop EDK processing cores that process live video streams.

#### **Guide Contents**

This user guide contains the following chapters:

- Chapter 1, "Video Starter Kit Overview" provides a kit overview with a brief description of the ML402 development platform, the VIODC, and the LVDS video camera.

- Chapter 2, "Developing Video Applications In System Generator" The Video Starter Kit provides for both simulation and real-time operation for each of the components in a video system.

- Chapter 3, "EDK Integration" details the design-flow for incorporating a

MicroBlaze™ processor into MVI framework. In particular, it describes using the EDK

processor block in System Generator and the automatically generated software

drivers to read and write data to the System Generator design.

- Chapter 4, "Hardware Co-Simulation" provides a description of the hardware co-simulation interfaces that make it possible to compile a System Generator diagram into an FPGA bitstream and associate this bitstream with a new run-time hardware co-simulation block.

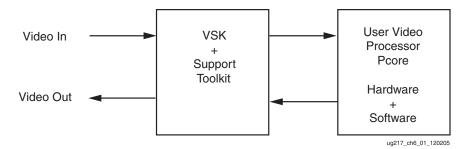

- Chapter 5, "VSK Diagnostics and Support Tool Kit" describes how the VSK diagnostics program serves to tie together the components of the VSK development toolkit into a program for configuring the ML402 and VIODC boards for video processing applications and for providing simple loopback and video processing functions. The VSK support toolkit consists of both hardware and software modules.

- Chapter 6, "VSK Tutorial" illustrates the process of creating a video *processing core* or pcore which is compatible with systems constructed with the Xilinx Embedded Development Kit (EDK). EDK pcores are reusable peripherals which can be imported into any EDK project.

- Chapter 7, "Compiling the VIODC FPGA Design" describes how to compile the System Generator vsk\_viodc\_xxx.mdl design to a bitstream (xxx is the version number).

- Appendix A, "VSK I/O Connector Location Pictures" contains pictures showing connection locations on the VIODC, LVDS video camera, the ML402 board, and the ML402 Evaluation Platform.

### **Additional Resources**

To find additional documentation, see the Xilinx website at:

http://www.xilinx.com/literature/index.htm.

To search the Answer Database of silicon, software, and IP questions and answers, or to create a technical support Web Case, see the Xilinx website at:

http://www.xilinx.com/support.

# **Conventions**

This document uses the following conventions. An example illustrates each convention.

## **Typographical**

The following typographical conventions are used in this document:

| Convention         | Meaning or Use                                                                                        | Example                                                                                            |

|--------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Courier font       | Messages, prompts, and program files that the system displays                                         | speed grade: - 100                                                                                 |

| Courier bold       | Literal commands that you enter in a syntactical statement                                            | ngdbuild design_name                                                                               |

| Helvetica bold     | Commands that you select from a menu                                                                  | File → Open                                                                                        |

|                    | Keyboard shortcuts                                                                                    | Ctrl+C                                                                                             |

|                    | Variables in a syntax<br>statement for which you must<br>supply values                                | ngdbuild design_name                                                                               |

| Italic font        | References to other manuals                                                                           | See the <i>Development System Reference Guide</i> for more information.                            |

|                    | Emphasis in text                                                                                      | If a wire is drawn so that it overlaps the pin of a symbol, the two nets are <i>not</i> connected. |

| Square brackets [] | An optional entry or parameter. However, in bus specifications, such as bus [7:0], they are required. | ngdbuild [option_name] design_name                                                                 |

| Braces { }         | A list of items from which you must choose one or more                                                | lowpwr ={on off}                                                                                   |

| Vertical bar       | Separates items in a list of choices                                                                  | lowpwr ={on off}                                                                                   |

| Convention          | Meaning or Use                            | Example                                    |

|---------------------|-------------------------------------------|--------------------------------------------|

| Vertical ellipsis   | Repetitive material that has been omitted | IOB #1: Name = QOUT' IOB #2: Name = CLKIN' |

| Horizontal ellipsis | Repetitive material that has been omitted | allow block block_name loc1 loc2 locn;     |

# **Online Document**

The following conventions are used in this document:

| Convention            | Meaning or Use                                             | Example                                                                                                         |

|-----------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Blue text             | Cross-reference link to a location in the current document | See the section "Additional<br>Resources" for details.<br>Refer to "Title Formats" in<br>Chapter 1 for details. |

| Red text              | Cross-reference link to a location in another document     | See Figure 2-5 in the <i>Handbook</i> .                                                                         |

| Blue, underlined text | Hyperlink to a website (URL)                               | Go to <a href="http://www.xilinx.com">http://www.xilinx.com</a> for the latest speed files.                     |

# Video Starter Kit Overview

# **Key Features**

- Standard Video Development Platform for Xilinx FPGAs

- Real Time HD video simulation using Xilinx System Generator's Hardware in the Loop

- Video Starter Kit (VSK) includes:

- Video I/O Daughter Card (VIODC) supports common video interfaces and standards

- ♦ ML402 board with FPGA development platform (Xilinx XC4VSX35 FPGA)

- LVDS Camera featuring Micron MTV022 automotive CMOS image sensor

- ◆ Xilinx System Generator Software (8.2) for VSK

- ♦ Xilinx ISE Software (v8.2) for VSK

- ◆ XIIinx EDK Software (v8.2) for VSK

- Application demos

- Video cables and power supply

- VIODC features:

- High Definition Component video input and output including 1080I, 720P, and 525P

- Standard Definition S-video and Composite video input and output

- Digital Video Interface (DVI) input and output up to 165 MHz

- VGA analog input and output up to UXGA

- SDI Serial Digital video interface input with cable equalizer and output cable driver. (The VSK is a demonstration platform only. For HD-SDI verification and compliance, Xilinx recommends using the Cook Technologies SDV board).

- LVDS camera input

- Software development features:

- System Generator Blockset for Mathwork's Simulink

- High-Speed Ethernet Hardware-in-the-Loop co-simulation provides near realtime video simulation

- High performance Multi-Port DDR memory controller

- ◆ Automatically create MicroBlaze™ video peripherals with memory mapped I/O

- ♦ Import MicroBlaze projects into System Generator models

#### **VSK Hardware Overview**

The Video Starter Kit hardware consists of a ML402 FPGA development platform with a VIODC and an LVDS video camera.

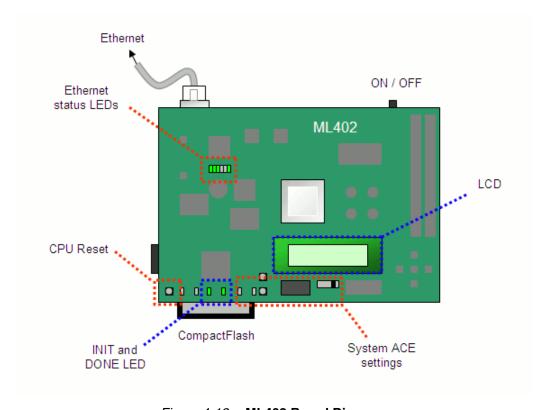

#### ML402 Development Platform

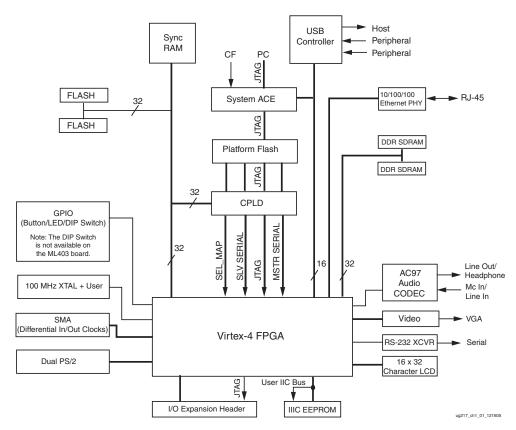

The VSK is based on the Virtex<sup>TM</sup>-4 ML402 XtremeDSP Evaluation Platform. The ML402 board contains a programmable XC4VSX35 FPGA and a number of standard peripheral interfaces, such as Ethernet, RS232, and DDR memory.

Figure 1-1: ML402 Block Diagram

#### XC4VSX35 FPGA

At the heart of the ML402 board is the XC4VSX35 FPGA, which contains both substantial logic resources (15,360 logic slices), dual port memory (192 x 18-Kbit block RAMs) and very high performance DSP blocks (192 DSP48 slices). In addition to high performance processing capability, the XC4VSX35 FPGA provides access to the VIODC card and the various external interfaces on the ML402 board.

# Gigabit Ethernet

The 10/100/1 Gigabit Ethernet port provides a link between the VSK and a PC for high speed video rate simulation. This high-speed simulation capability is known as Hardware-in-the-Loop Co-Simulation. Simulation rates up to 600 Mb/s are achievable.

#### RS-232 Port

The RS-232 port provides a link to a PC terminal program, such as HyperTerminal. Used for debugging and controlling a MicroBlaze™ embedded processor. It must be connected to the PC using a NULL modem cable.

#### **DDR Memory**

A 267 MHz 32-bit wide DDR memory is used to store video frames.

## System Ace Controller

The System Ace controller provides access to Compact Flash memory cards which are used to hold demos and bootable FPGA configurations.

## I/O Expansion Header

The 64-signal pin expansion header is used to connect to the VIODC. For more information on the ML402 board, refer to the ML402 webpage on the Xilinx website.

## Video Input and Output Daughter Card

The VIODC is a standard video interface card for Xilinx development platforms. It is compatible with the ML401, ML402, ML403 boards and other future Xilinx development platforms.

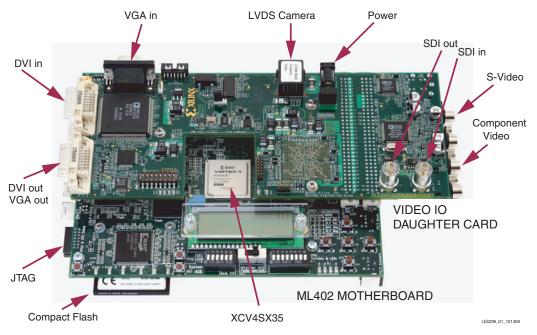

The VIODC is shown in Figure 1-2 with the video ports labeled. The VIODC provides access to high definition and standard definition video streams as well as computer graphics video interfaces, such as VGA over DVI and SDI interfaces. The following interfaces are supported.

Figure 1-2: VIODC and ML402 Board with Video Interface Ports Labeled

#### LVDS Camera Input

The LVDS camera input port supports the <u>Irvine Sensors</u> LVDS RGB Camera with a <u>Micron</u> MT9V022 1/3 inch CMOS image sensor. The camera provides 752 x 480 pixels at 60 Hz progressive scan. It features low noise and very high dynamic range. The interface is implemented using LVDS signaling over standard Cat-6 Ethernet cables. Note that the LVDS camera interface is not compatible with Ethernet.

#### Component Video I/O

The Component Video I/O uses standard RCA connectors to provide High Definition (HD) video to the VIODC. Component Video is encoded as YPbPr video channels. The Component Video input on the VIODC supports 1080I, 720P, and 525P video standards. The Component Video interface devices on the VIODC support 10-bit digital video.

#### DVI Digital Video I/O

The VIODC supports DVI video input and output. DVI is commonly used to interface to flat panel displays and computer graphics cards. The VIODC DVI interfaces support up to 165 MHz pixel clocks. In addition to computer graphics, DVI is also used to carry HD video and is commonly found in high-end consumer video equipment, such as plasma displays, and can be found on some DVD players. The DVI ports can also be connected to HDMI interfaces by using a simple adapter.

#### S-Video and Composite Video

The VIODC supports S-Video inputs and outputs. These interfaces can be configured to support NTSC, PAL, and virtually any other Standard Definition (SD) video format.

#### SDI Video Interface

A complete SDI video interface capable of supporting both SD and HD SDI is included with the VIODC. The SDI standard is a high-speed serial interface used to carry video over coax cable. It is generally used in a studio environment. The SDI system includes cable equalizers and genlock circuitry. (The VSK is a demonstration platform only. For HD-SDI verification and compliance, Xilinx recommends using the Cook Technologies SDV board).

#### XCV2P7 FPGA

The VSK also includes a Xilinx XCV2P7 FPGA, which is used to interface to the various video interfaces, as well as the ML402 main board. It features Multi-Gigabit Transceivers (MGTs), which are used to support the SDI interface. It also enables the VIODC to be used in a stand-alone fashion.

20

# **VSK Demo Application**

Several demo applications are included with the VSK. One demo (Figure 1-3) shows how the VSK can be configured as a video processor. This demo application is included in the VSK\_diagnostics design included in the VSK examples directory. It can be used to apply some common video filters to the video from the RGB LVDS camera or other video sources.

Figure 1-3: RGB Camera Demo Setup

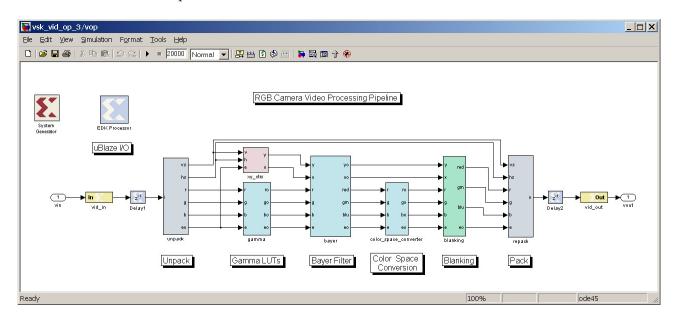

Figure 1-4 illustrates a common video processing pipeline. The design implements a sequence of video operations including gamma correction, Bayer filtering, and color space correction. It is implemented using the System Generator blockset for MATLAB Simulink. System Generator is used to export this design as an EDK pcore, which is a standard Xilinx peripheral for embedded processors. After a pcore is created, it can be used in any Xilinx EDK project. Any EDK project can use a pcore, even if they are targeted to other development boards or FPGAs.

Figure 1-4: RGB Camera Video Processing Pipeline

The RGB camera processing pipeline design has a video input and a video output port. In the complete application, these video buses are connected to other process implementing

video processing, memory or I/O to the VIODC. The block diagram of the VSK diagnostics program is shown in Figure 1-5.

Figure 1-5: Block Diagram of VSK RGB Camera Demo Included in the VSK

For this application, the embedded MicroBlaze processor is used to configure the video processing pipeline. It communicates with memories and registers in the video pcores via System Generator shared memory primitives. The hardware logic and software drivers required by MicroBlaze to communicate with the shared memories in the pcore are automatically generated by System Generator during compilation.

The video processing demo is included in a poore named vop for Video Op. The Sysgen design is named vsk\_vid\_op\_6.mdl. This demo is part of the VSK diagnostic program and can be found in the VSK examples directory. For more information, refer to Chapter 5, "VSK Diagnostics and Support Tool Kit."

# Software and Application Updates Available Online

VSK software and applications are supported by a <u>VSK web page</u> and the latest software and applications versions can be found there. The software support is integrated into System Generator and will be upgraded as new System Generator versions are released. New applications for the VSK will be posted on the VSK web page as they are developed.

# **Software Support Package Overview**

The VSK includes hardware, software, and applications. Xilinx software is used to create applications which run on the VSK and Xilinx FPGAs. Three basic software flows are supported. These are illustrated in Figure 1-6, Figure 1-7, and Figure 1-8.

Figure 1-6: Software Simulation Flow

#### Software Simulation

In the first flow, called software simulation, Simulink designs that are constructed from the System Generator blocks are compiled and run in MATLAB Simulink. Figure 1-6 shows the software flow for software simulation. This flow is quick and easy to develop and offers good performance using the built-in MATLAB floating-point matrix operations. Larger systems, however, slow down significantly, and it is difficult to use this approach with live video streams. Additionally, problems occur when the design is implemented in fixed-point blocks for FPGA implementation. This can result in very low pixel rates due to poor simulation performance, often requiring hours per frame of video.

### Hardware Implementation

The second software flow (Figure 1-7) compiles the user's design to hardware and runs the hardware on the VSK video development platform. This allows the video IP to be tested using live video streams.

Figure 1-7: Real-Time Deployment Flow

#### Hardware Co-Simulation

The third type of software flow (Figure 1-8) is a hybrid of the software simulation and hardware deployment called Hardware-in-the-Loop co-simulation. In it, the bulk of the design is generated as in the real-time deployment flow. However, hardware data streams can be routed to the Simulink software simulation using the Xilinx System Generator Hardware co-sim engine.

The advantage of this mode is that small video filters which are part of a larger video processing system can be run in simulation, while the bulk of the video system is implemented in real time hardware. If buffering is employed, the software simulation can operate on stored video frames from the video stream at a reduced frame rate. Using the Ethernet Co-Simulation, near real-time video rates can be achieved. This translates to a few frames per second using  $640 \times 480$  video.

Figure 1-8: Hardware-in-the-Loop Flow

The pre-generated bitstream and co-sim subsystem can be generated from another system generator diagram or it can be an existing EDK project. The user can use the EDK import feature in System Generator to import an EDK project as a co-sim block.

# **VIODC HDL Support Package**

While the above software flows leverage the advantages of developing video IP in System Generator/MATLAB/Simulink, users may prefer to use traditional HDL design flows. The Video Starter Kit also includes two demonstrations written in Verilog. These examples exercise all the video functions on the VIODC and are generally self-explanatory. In addition, these demos can run on a stand-alone VIODC board.

Refer to the DVI, VGA, and Component Video Demonstration User Guide and the SDI Video Demonstration User Guide for further information.

# **System Generator Support**

System Generator includes several features that are useful for developing video applications with the Video Starter Kit. These are outlined below and additional documentation for each of these features can be found in the VSK document package. In addition, tutorials are included in the examples directory to assist in learning to use these powerful features.

# **DDR Memory Controller**

The VSK includes a capable multi-port memory controller. The controller supports the DDR memory on the ML402 board. It can also be targeted to other boards and is fully configurable for port size and number of ports. The controller contains a simulation model and can be run in HDL co-simulation mode, or compiled to run in real time and as part of hardware co-simulation block.

#### Pcore Export and EDK Import

Pcore export is a new method of generation from Simulink diagrams that allows the user diagram to be imported into any EDK project as a Pcore. Conversely, EDK import allows EDK projects to be imported into System Generator diagrams. Pcore export is used to generate the three pcores in the VSK diagnostic demo from System Generator diagrams.

## Multiple Subsystem Generator

The Multiple Subsystem Generator flow allows System Generator models to include multiple clock domains. This flow is used to generate the design for the VIODC FPGA, which is included in the VSK diagnostics program.

#### **Ethernet Co-Sim**

High-speed Ethernet co-sim and point-to-point Ethernet co-sim are supported by the System Generator for the VSK. To achieve near real-time video rates, reusable buffer blocks are included in the Ethernet demos that are included in the VSK.

#### **Diagnostics**

A diagnostics program called the vsk\_diagnostics is included with the VSK. Refer to Chapter 5, "VSK Diagnostics and Support Tool Kit" for more information. The diagnostics include System Generator designs for the VIODC FPGA, and three pcores integrated into an EDK project for the ML402 FPGAs. They also include software routines to configure the video interface chips on the VIODC and to control the video processing pcore, video interface pcore, and DDR memory pcore.

#### **Demonstrations**

Several demonstration designs are included with the VSK.

#### MPEG Decoding Demo

The VSK diagnostics include an MPEG-4 demo, which can be run from the Compact Flash. Refer to the *Video Starter Kit Quick Start Guide* (*UG239*) and the *MPEG-4 Demonstration User Guide* (*UG234*) for more details.

#### VSK Diagnostics Camera Demo

The VSK diagnostics also include a camera demo, which can be run from the Compact Flash. Refer to *Video Starter Kit Quick Start Guide* (*UG239*) and Chapter 5, "VSK Diagnostics and Support Tool Kit" for more details.

#### SDI Demo

A demo featuring the SDI interface and written in Verilog is available for the VIODC. Refer to the documents SDI Video Demonstration User Guide in the VSK document package for further information.

## Video Demo in Verilog

A demo which exercises all the video interfaces on the VIODC is available. Refer to the documents *DVI*, *VGA*, and *Component Video Demonstration User Guide* in the VSK document package for further information

# Developing Video Applications In System Generator

#### **Overview**

Figure 2-1 shows a typical video processing system. In this system, a microprocessor is used to control a video pipeline consisting of a video source and sink, a large memory for storage of video data, and a video processing system.

Figure 2-1: Video System Diagram

As the video system is being developed, these functions can be implemented in real hardware or in simulation. Simulation of video processing applications creates special challenges for simulation due to both the real-time nature of video streams and the enormous amount of video data required per frame.

Typically, video development requires real-time hardware to prove the video operation on real-time data streams, as well as a simulation environment to develop and test the video processing components. The Video Starter Kit (VSK) provides both for simulation and real-time operation for each of the components in a video system.

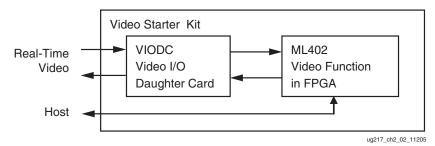

# **Real-Time Operation**

Real-time operation (Figure 2-2) is provided by the combination of the VIODC and ML402 development boards. The VIODC provides video sources and sinks to the ML402 and the ML402 is used for real-time processing of the video streams. The ML402 board includes a state of the art Xilinx Virtex-4 FPGA for real-time video processing, memory, and communications peripherals. Video memory is provided on the ML402 board in the form of DDR SDRAM memory. The ML402 board supports a MicroBlaze processor with a

standard set of peripherals. Host communications can be supported over RS-232, USB, or Ethernet ports.

Figure 2-2: Real-Time Video Processing

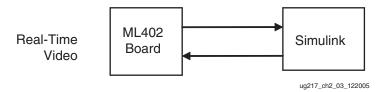

# Hardware-in-the-Loop Video Simulation

FPGAs are software programmable, yet they have the unique ability to operate on real-time video streams at clock rates well over 300 MHz. Using FPGAs to process real-time data during algorithm development is known as Hardware-in-the-Loop Co-Simulation. Hardware-in-the-Loop Co-Simulation (also known simply as hardware co-sim) can be used to quickly demonstrate video processing functions at real-time rates.

Figure 2-3: Hardware-in-the-Loop Video Processing

# Hardware-in the Loop Co-Simulation

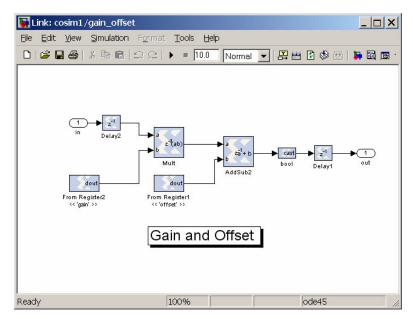

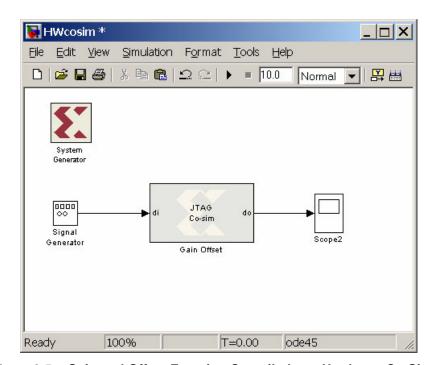

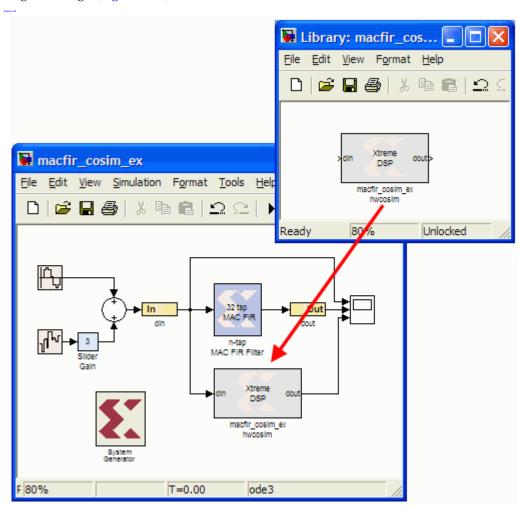

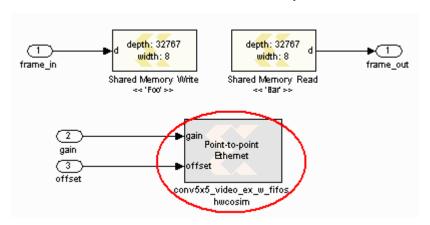

Xilinx System Generator provides the ability to replace Simulink subsystems with a *hardware co-sim* token. For example, the Figure 2-4 shows a video processing block which implements a gain and offset function on a single video channel. In Figure 2-5 the video processing block has been compiled into a hardware co-sim block.

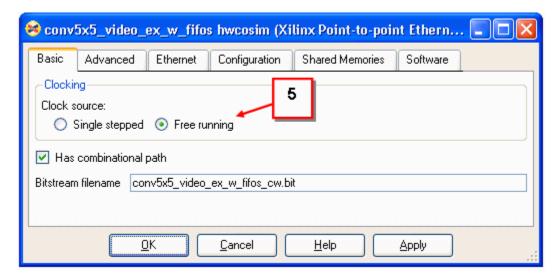

When the Simulink Play button is pressed to start simulation, the FPGA design containing the gain and offset function is loaded to a development board such as the ML402. Then data is passed from the Simulink source to the function in the FPGA, the clock is stepped automatically, and output data is passed back to the Simulink scope.

Hardware co-sim can also be used with buffer blocks to substantially increase data bandwidth and throughput. When used with Mathworks Video and Image Acquisition Blockset, hardware co-sim can be used to provide non-real-time video simulation.

Figure 2-4: Simulink Diagram Implementing a Gain and Offset Function Using Xilinx System Generator Blocks

Figure 2-5: Gain and Offset Function Compiled to a Hardware Co-Sim Token

# **Software Simulation Modes**

During development, it is very useful to be able to simulate video processing blocks using real video data streams. Software simulation (shown in Figure 2-6) is supported for the VSK using Mathworks Simulink software in conjunction with the Xilinx System Generator. During simulation, real-time operation is simulated by operating on captured video in the

video memory at reduced video clock rates. Although software simulation is not as fast as real-time hardware operation, Simulink provides a quick and facile method of developing and testing video processing functions. In addition, standard video processing functions available for Simulink, such as the Image Processing Toolbox, allow video processing functions to be quickly prototyped and tested.

Figure 2-6: Software Simulation Using Live Video Signals with Simulink

The infrastructure required to source and sink video streams from the VSK to the Simulink simulation is provided by the Xilinx System Generator co-simulation feature, which allows simulation diagrams to communicate directly with hardware. System Generator also provides the ability to simulate flowgraphs constructed from Xilinx Blockset components, as well as VHDL and Verilog *black boxes* using HDL simulators such as ModelSim.

# **Hardware-Software Systems**

Video systems often require a control processor. The processor typically is used to communicate with a host system, set up video processing operations, compute coefficients and generally operate as a low rate data processor. Xilinx System Generator and the Embedded Development Kit (EDK) software tools can be used together to implement and simulate a system with a processor and FPGA video processor functions operating on live video streams.

#### Generating a Video Processor as an EDK Pcore

The Xilinx EDK can be used to construct processor systems with integrated memory and peripherals. Processor peripherals, such as memory and Ethernet interfaces, can be included into EDK projects and are known as processor cores or *pcores*. Xilinx System Generator can be used to generate custom pcores for functions such as video processing. Figure 2-7 illustrates a processor system with standard and custom peripherals. The processor is used to configure the video processing pipeline, and video data is passed directly between stages of the video pipeline. This particular configuration with three custom pcores is used for the VSK camera processing demo, VSK, and the VSK diagnostics.

Figure 2-7: MicroBlaze Processor with Peripherals and Three Custom Video Peripherals

The above system can be used to implement and test video peripherals. After developed and validated, a prore peripheral is able to be incorporated into any EDK system. System Generator can be used to construct and test EDK prores. This facility is available as the EDK Export compilation target in System Generator.

#### **Hardware-Software Communication**

## Memory Mapped Hardware

Hardware is often controlled by software programs. This requires communication channels between the hardware peripheral and the software program. System Generator includes special register, FIFO, and memory blocks which can be automatically mapped into the processor's function space. These blocks are termed *shared memories* because they are shared between the processor and the System Generator model diagram. These blocks make it simple to use a processor to read and write hardware memories. See Figure 2-8.

Figure 2-8: System Generator Shared Memory Blocks

# MicroBlaze Processor Communicating with a Shared Memory

When a diagram (shown in Figure 2-9) containing shared memory blocks is compiled as a EDK pcore, the shared memory objects are mapped into the function space of the C program, using an FSL communications link.

Figure 2-9: MicroBlaze Processor Communicating with a Shared Memory

#### Hardware-Software Co-Simulation

Often both hardware and software are developed concurrently. The development of video processing peripherals generally require the development of both hardware and software drivers for the hardware. This task is eased if software co-simulation is available as hardware is simulated. Hardware-software co-simulation is available as part of System Generator hardware co-simulation. This facility is named EDK co-simulation.

#### **EDK Co-Simulation**

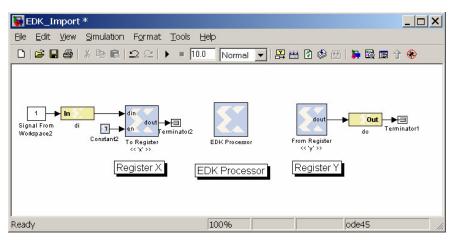

System Generator allows for the incorporation of a MicroBlaze block into a Simulink diagram. When a System Generator diagram that includes a MicroBlaze block is compiled and run under hardware co-simulation, the processor is able to communicate with any shared memory objects which are also in the diagram. For example in Figure 2-10, the MicroBlaze processor is able to read from register X and write to register Y. In addition, a C header file containing function calls is generated to allow for easy communication with shared memory objects.

Figure 2-10: EDK Import with Registered IO

If the EDK project includes a Serial Port, the user can interact with the processor via the RS-232 interface.

# **VSK Video Processor Development System**

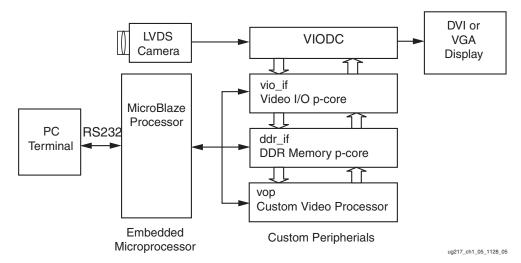

The VSK can be used to develop video processing peripherals as EDK pcores. To abstract the low level details of the video processing, a pre-built system called VSK1 has been developed to provide video streams directly to a user pcore. It includes a processor and pcores to interface to the VIODC and DDR memories and process video. These pcore designs can be used as is or modified to create new pcores.

The ML402 board and the VIODC are configurable hardware systems which both contain FPGAs. FPGA designs written in System Generator have been developed for each of these FPGAs, and MicroBlaze software drivers have been developed to provide access to the various functions incorporated into the FPGAs. These FPGA designs and software drivers are used in the VSK diagnostics and demos. As a set, they provide a video pcore development environment for Video processors and are described in the following sections.

#### ML402 FPGA

The ML402 software and hardware are partitioned into a MicroBlaze and three pcores.

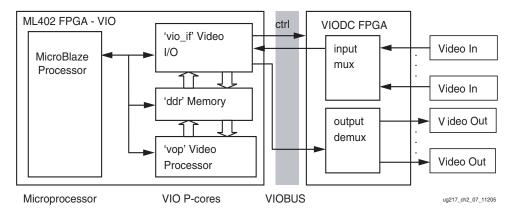

Figure 2-11: ML402 FPGA

#### MicroBlaze Subsystem

The MicroBlaze subsystem consists of a simple MicroBlaze processor, a 64-KB internal memory and an RS-232 system. It can be extended to include access to external SRAM and the various peripherals on the ML402 board.

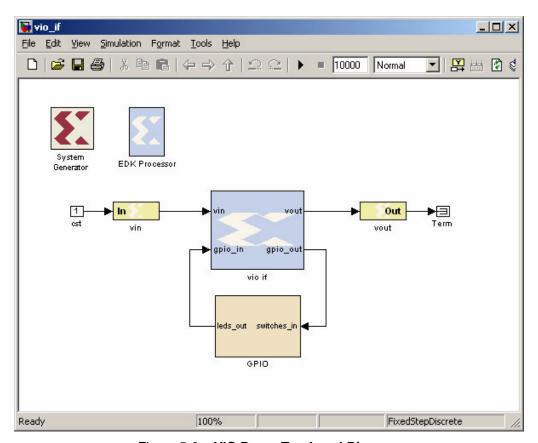

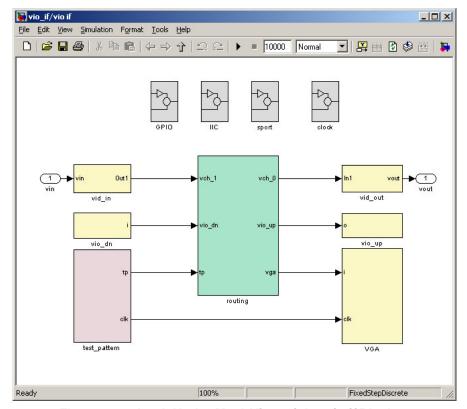

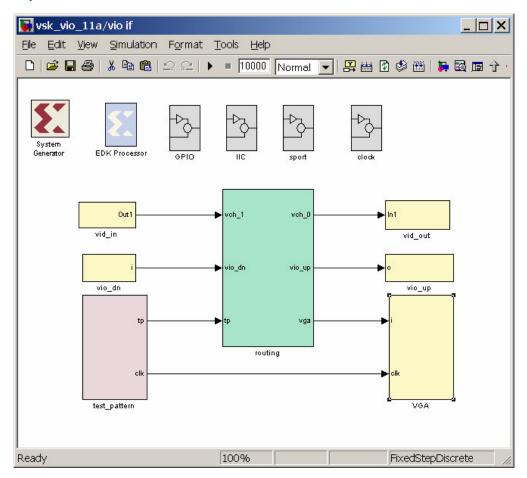

#### vio if Pcore

The vio\_if pcore is used to communicate with the VIODC over the vio bus. It supports one video input and one video output bus. Each video bus is 26 bits plus a pixel enable. This vio\_if pcore also provides IIC communication to the devices supported by the VIODC FPGA, as well as a small serial bus to communicate with internal VIODC registers.

#### ddr\_if Pcore

The ddr\_if provides access to DDR memory. It is designed to store and playback video sequences and provide access to the MicroBlaze. The DDR provide is built around the Multiport System Generator DDR Memory controller.

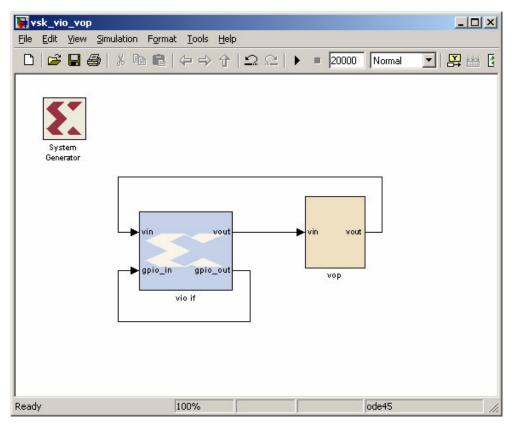

#### vop Pcore

The pcore labeled vop is the pcore which contains a basic video processing pipeline. The MicroBlaze project provides video input and output streams to the core. The existing core can be replaced if modified to develop a new video processor.

#### VIODC FPGA

The Video Starter Kit contains an XCV2P7 FPGA on the VIODC. An FPGA design has been developed to allow the MicroBlaze processor to configure the various video interface ICs and select from among the various video sources. The VIODC connects to the ML402 board over a 64-pin interface bus. This bus is named the VIOBUS.

The VIODC provides an interface to the various video interface ICs and routes video to and from the ML402 FPGA.

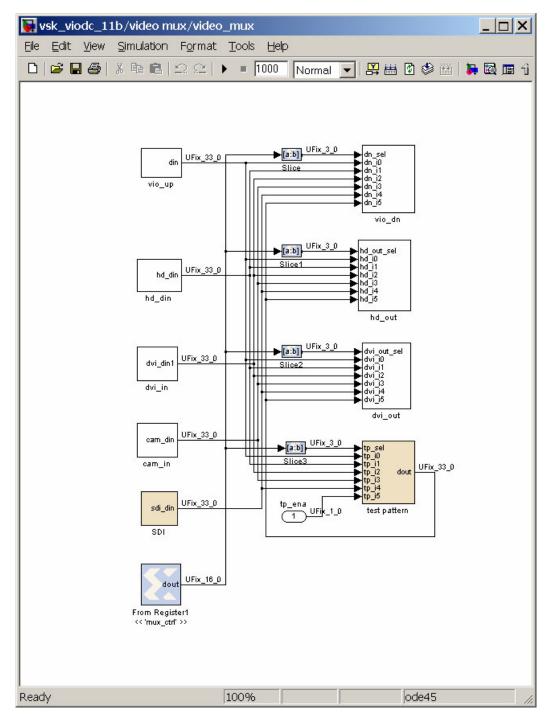

#### Video Sources

The VSK allows for various video source to be used to source a video stream. Live video streams are piped down from the VIODC card. The VIODC supports VGA, DVI, SDI, HD component video, SD S-video, and composite video. In addition, test patterns can be used to create live video streams. When the viodc.bit FPGA program is loaded to the VIODC, video sources available from the VIODC can be selected by configuring the VIODC using the MicroBlaze. (SDI video input is not available in version 1 of the VIODC program). During simulation, video sources can include MATLAB matrices and MATLAB Simulink Image Processing Blockset video sources.

#### Video Sinks

The Video Starter Kit allows video streams to be driven to any of the video output ports. The VIODC supports VGA, DVI, SDI, HD component video, SD S-video, and composite video outputs. When the viodc.bit FPGA program is loaded to the VIODC, video sources available from the VIODC can be selected by configuring the VIODC using the MicroBlaze. During simulation, video can also be routed to MATLAB matrices and MATLAB Simulink Image Processing Blockset video displays.

An additional VGA output suitable for VGA or 525P video output is provided on the ML402 FPGA. It can also be used as a diagnostic display.

# EDK Integration

#### **Overview**

Embedded processors are important components inside any MVI system. The Xilinx Embedded Development Kit (EDK) is an integrated software solution for designing embedded processing systems, and the MicroBlaze™ 32-bit soft-processor core is supported by the EDK. This chapter details the design-flow for incorporating a MicroBlaze processor into MVI framework. In particular, it describes using the EDK processor block in System Generator and the automatically generated software drivers to read and write data to the System Generator design.

Two methods are described:

- System Generator design exported into an EDK system

- EDK project imported into a System Generator design for hardware co-simulation.

Communication between an EDK processor and the System Generator design is accomplished via shared-memories—registers, FIFOs, and RAMs.

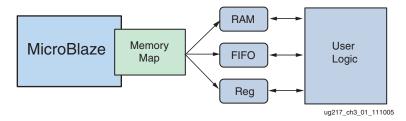

## MicroBlaze Processor Interface

The MicroBlaze processor interface is exposed through the EDK processor block provided by System Generator. Figure 3-1 shows the communication between user-defined logic and the MicroBlaze processor.

Figure 3-1: Memory-Mapped User Logic

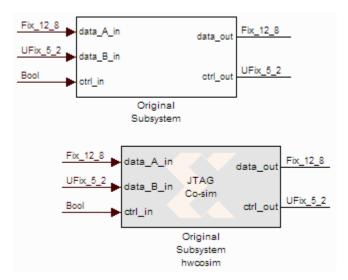

Memories used in a user's design form the processor interface into the user-logic. These memories are *associated* with a MicroBlaze processor through the EDK processor block's GUI interface. After an association is made, System Generator automatically creates a memory-map that marshals data to and from the processor. Memories that are associated to the processor can be accessed using C-code device drivers automatically generated by System Generator.

#### **EDK Pcore Export Mode**

When used in prore export mode, the memory map block shown in Figure 3-1 and all the blocks to its right are packaged into a prore peripheral. Software drivers and documentation for the memory-map interface are also generated and delivered with the peripheral.

#### **EDK Import Mode**

When used in EDK import mode, an EDK project file is imported into System Generator by running the EDK Import Wizard. When the import wizard completes, the EDK system is pulled into the System Generator design as a black-box. During the import process, the EDK system is augmented with Fast Simplex Link (FSL) interfaces that communicate with the memory-map shown in Figure 3-1.

# Adding a Processor to a System Generator Design

#### The EDK Processor Block

A processor can be added to a System Generator design by using the EDK processor block, which can be found in the System Generator Index and Control logic libraries. Figure 3-2 shows an image of the EDK Processor block.

Figure 3-2: EDK Processor Block

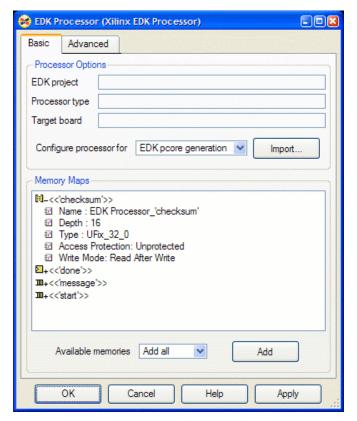

Double clicking the block opens the block's GUI, shown in Figure 3-3. Refer to the *System Generator User Guide* for a more detailed explanation of the GUI.

# Interfacing the EDK Processor to User Logic

Shared-memories instanced in a user's design can be associated to an EDK Processor by adding that memory into the processor's memory map. Figure 3-3 shows an EDK Processor block with four shared memories added to the memory-map: a RAM, a register, and two FIFOs. Memories visible to the EDK processor are listed in the *Available Memories* pull-down menu. Selecting a memory and pressing the Add button adds that memory into the processor's memory-map. Right-clicking on the *Memory Maps* tree-view reveals a popup menu that provides services, such as allowing memories to be removed from the memory map and re-syncing the memory map. Re-syncing a memory map regenerates the decoder logic used to marshal data to their respective memories.

Figure 3-3: EDK Processor GUI

## Exporting the Design as a Pcore

The Xilinx Platform Studio (XPS) is a tool that is shipped with the EDK. XPS is an integrated development environment that allows a processor to be created, configured with IP, and for software to be written and compiled into the processor's bitstream. When configuring a processor in XPS, a user is presented with a list of available IP that can be connected to a processor. Each IP that can be added on as a peripheral to a processor must be packaged as a pcore. System Generator provides a compilation target that compiles a user design into a pcore.

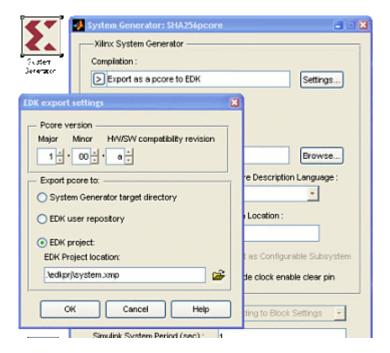

To export a user design as a pcore, the EDK processor block must be used in conjunction with the *Export as a pcore to EDK* compilation target found in the System Generator block. The EDK processor must to be configured for EDK export mode. This is done by setting *Configure Processor For* to *EDK Pcore Generation* as shown in Figure 3-3.

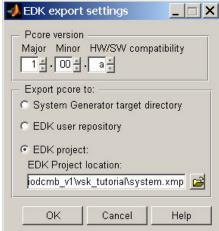

After configuring the EDK processor, an EDK pcore can be generated by using the System Generator compilation GUI. Refer to Figure 3-4. Double click on the System Generator block and set *Compilation* to *Export as a pcore to EDK*. Press the *Settings*... button to bring up the EDK Export Settings dialog box. This controls where the pcore is exported to and assigns a version number to the pcore.

Refer to *System Generator Compilation Types* chapter in the *System Generator User Guide* for more detailed information on the EDK export compilation target.

Figure 3-4: Export as a Pcore to EDK

The pcore compilation process produces a collection of files organized in a specific directory structure. The files and directory structure are listed in Table 3-1.

Table 3-1: Pcore Directory Structure

| Directory<br>Name      | File Type/<br>Extension | Description                                                                                                                                                                                    |

|------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| data                   | mdd, mpd<br>pao, tcl    | Data files used by the EDK to configure a pcore. The mdd and tcl files are used by LibGen to generate device drivers for the pcore. The mpd and pao files describe the interface of the pcore. |

| doc                    | pdf                     | An Adobe PDF file documenting the memory-<br>map interface and also providing information and<br>examples on how to read and write to the pcore.                                               |

| doc/html/api           | html                    | An html version of the PDF file.                                                                                                                                                               |

| hdl<br>vhdl<br>verilog | vhd<br>v                | hdl directory contains two other directories:<br>VHDL files used by the pcore.<br>Verilog files used by the pcore.                                                                             |

| netlist                | edn, ngc                | Precompiled netlists used in the pcore.                                                                                                                                                        |

| src                    | Makefile, c, h          | Template C header and source files used during device driver generation.                                                                                                                       |

A tutorial showing this design-flow can be found in the Hardware Software Co-Design in System Generator chapter in the *System Generator User Guide*.

## Importing an EDK Project into System Generator

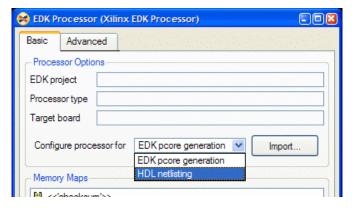

A project created in the EDK can be imported into a System Generator project by using the EDK Import Wizard. Projects imported using the wizard can only contain one MicroBlaze processor. The EDK Import Wizard can be launched through the EDK processor block GUI

Figure 3-5 shows one way to launch the EDK Import Wizard. If the EDK project string is empty, selecting *HDL netlisting* in the *Configure processor for* parameter launches the EDK Import Wizard.

Figure 3-5: Launching Import Wizard

If an EDK project has been imported previously, the EDK project field contains the path to the project that has been imported. If the processor configuration for that project has changed, the import wizard should be rerun. This can be achieved by clicking on the Import button.

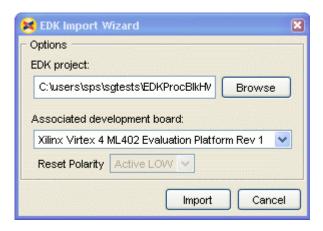

The EDK Import Wizard (Figure 3-6)modifies the given EDK system by adding in a pair of FSL FIFOs that will be used by the memory map created by the EDK processor block when shared-memories are associated with the processor. The EDK is next called upon to create the processor netlist. Finally, the EDK Import Wizard creates the wrapper and associated configuration files required for the netlists to be imported into System Generator. Following this, when the EDK processor block is configured for *HDL netlisting*, System Generator is capable of generating netlists containing the MicroBlaze processor. This allows designs containing a MicroBlaze processor to be compiled for hardware cosimulation.

Figure 3-6: EDK Import Wizard

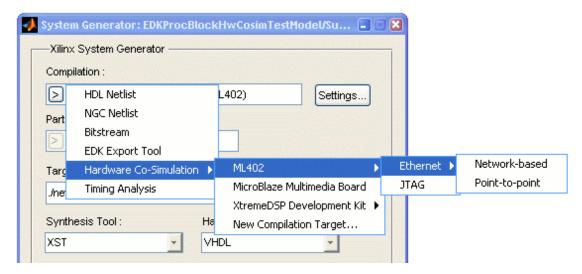

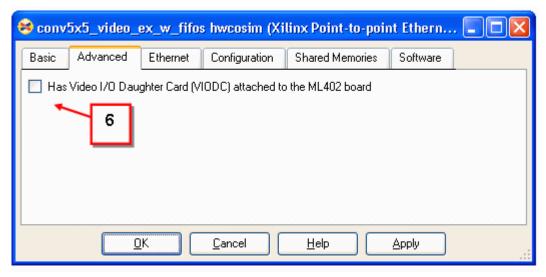

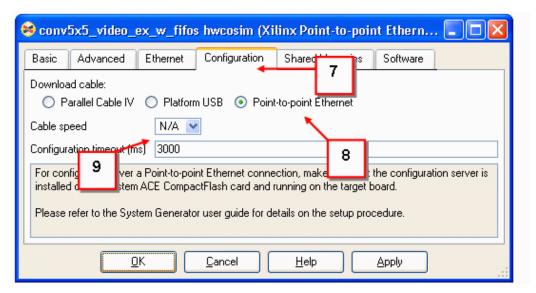

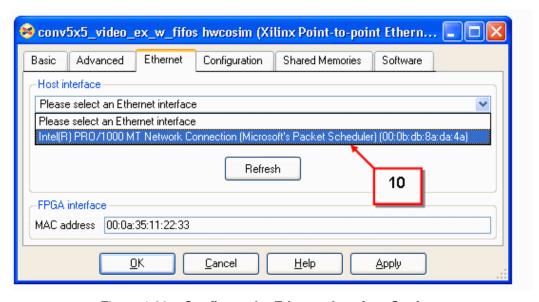

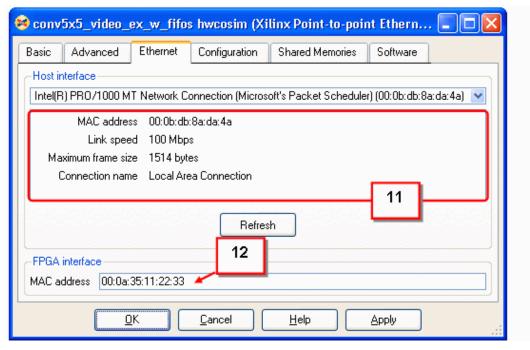

An EDK Processor block can be compiled into a co-simulation block by selecting one of the hardware compilation targets available, as shown in Figure 3-7. For the ML402 board, three options are available: JTAG, network-based, and point-to-point. For information on hardware co-simulation, refer to Chapter 4, "Hardware Co-Simulation."

Figure 3-7: Hardware Co-Simulation Options

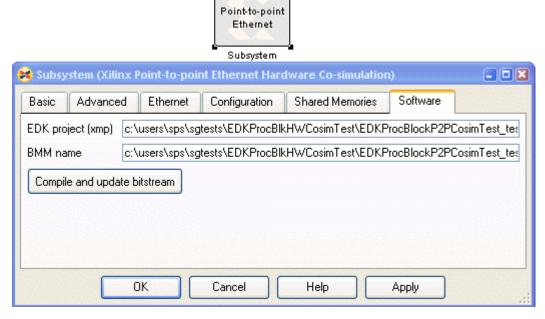

If an EDK processor block is detected during generation of a hardware co-simulation block, the *Software* tab of the co-simulation block's GUI becomes active (Figure 3-8). The Software tab contains path locations to EDK Project and also to the Block Memory Map (BMM) file that was generated with the co-simulation block. The BMM file is used by the EDK to update the processor with compiled C code.

Figure 3-8: Software Tab

Code written in the EDK Project can be compiled and updated into the co-simulation block by using the *Compile and update bitstream* button in the Software tab.

A tutorial showing this design-flow can be found in the "Hardware Software Co-Design in System Generator" chapter in the *System Generator User Guide*.

## **Writing Software Code**

Shared-memory blocks associated to an EDK Processor can be accessed by name inside C code. When System Generator creates the memory map, template C-code software drivers and their corresponding documentation are created. This C-code driver is inflated by the EDK during the LibGen phase of compilation in the EDK software compilation flow.

The documentation generated for a prove can be found in the doc directory in a prove. A PDF and an HTML version of the documentation are provided, and these can be accessed from the EDK.

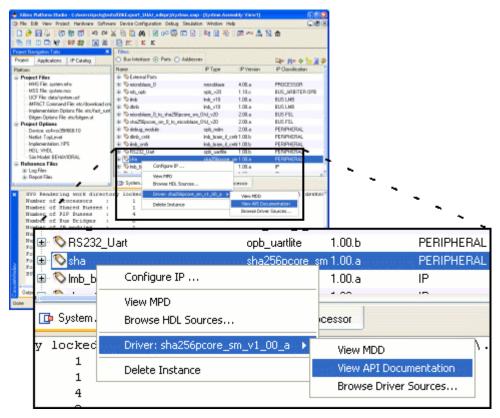

Figure 3-9 shows a screen capture of a Xilinx Platform Studio (XPS) instance. The peripheral sha256pcore\_sm is a pcore generated with System Generator. In this EDK project, that pcore has been added to the system and renamed sha. Right click on the peripheral in the XPS assembly view to call up the popup menu shown in Figure 3-9. Selecting *View API Documentation* shows the documentation for the peripheral. The documentation contains information on which header files to include, the naming convention of the memory-map identifiers, the software driver function prototypes, and example code snippets.

Figure 3-9: Xilinx Platform Studio - Assembly View

The generated software drivers contain six basic functions for accessing shared memories. The <inst> label in the function list shown below refers to the instance name of the pcore. When a user-defined pcore is added into an EDK project, a unique instance name

41

42

can be given to that pcore. In Figure 3-9 shows a pcore that has been named sha. As such, when reading data from that peripheral, the read function is sha Read().

When an EDK project is imported into System Generator, the EDK Import Wizard automatically configures the system with a stub peripheral representing the communications between the EDK and the System Generator peripheral. The peripheral is named  $xlsg_iface$ . As such, when reading data from that peripheral, the read function is  $xlsg_iface$ . Read().

```

int <inst> Read

(unsigned int memName,

unsigned int addr,

unsigned int* val)

int <inst> ArrayRead (unsigned int memName,

unsigned int startAddr,

unsigned int transferLength,

unsigned int** valBuf);

int <inst>_Write

(unsigned int memName,

unsigned int addr,

unsigned int val);

int <inst>_ArrayWrite (unsigned int memName,

unsigned int startAddr,

unsigned int transferLength,

const unsigned int* valBuf);

unsigned int <inst>_GetFifoDataCount (unsigned int memName);

unsigned int <inst> GetFifoEmptyCount (unsigned int memName);

```

Figure 3-10 shows a snippet of the automatically generated documentation. This shows that the pcore has four shared-memories that can be accessed: a register, two FIFOs, and a RAM. The first column shows the name of the shared-memory, as defined in the System Generator diagram. Column 3 shows the identifiers that should be used in the C-code drivers.

| Shared Memory<br>Name | Native<br>Precision* | ldentifier**                                 | Notes        |

|-----------------------|----------------------|----------------------------------------------|--------------|

| done                  |                      | <inst>_DONE</inst>                           | FromRegister |

|                       | UFix_1_0             | <inst>_DONE_DOUT</inst>                      | Read only    |

| message               |                      | <inst>_MESSAGE</inst>                        | ToFIFO [31]  |

|                       | UFix_32_0            | <inst>_MESSAGE_DIN</inst>                    | Write only   |

|                       | UFix_5_0             | <pre><inst>_MESSAGE_PERCENTFULL</inst></pre> | Read only    |

|                       | UFix_1_0             | <inst>_MESSAGE_FULL</inst>                   | Read only    |

|                       | Boolean              | <inst>_MESSAGE_RST</inst>                    | Write only   |

| start                 |                      | <inst>_START</inst>                          | ToFIFO [15]  |

|                       | UFix_1_0             | <inst>_START_DIN</inst>                      | Write only   |

|                       | UFix_4_0             | <inst>_START_PERCENTFULL</inst>              | Read only    |

|                       | UFix_1_0             | <inst>_START_FULL</inst>                     | Read only    |

|                       | Boolean              | <inst>_START_RST</inst>                      | Write only   |

| checksum              | UFix_32_0            | <inst>_CHECKSUM</inst>                       | RAM [0:15]   |

Figure 3-10: Memory Map Documentation

For instance, reading from the memory called *checksum* should be done as follows:

```

sha_Read(SHA_CHECKSUM, 0, &val);

```

The memory name to read from is <INST>\_CHECKSUM. In this case, the instance of the pcore is sha. Reading should be done from address 0 of that shared memory and the result placed into the register called val.

When reading and writing to RAMs, the address is specified as an index into that memory. When reading and writing to registers and FIFOs, address refers to their address in the memory map. For instance, reading the percent full port of the memory named message is performed with the following code:

```

sha_Read(SHA_MESSAGE, SHA_MESSAGE_PERCENTFULL, &val);

```

The memory name to read from is SHA\_MESSAGE and the address to read from is SHA\_MESSAGE\_PERCENTFULL.

## Hardware Co-Simulation

### **Hardware Co-Simulation Overview**

System Generator provides hardware co-simulation interfaces that make it possible to compile a System Generator diagram into an FPGA bitstream and associate this bitstream with a new run-time hardware co-simulation block. A run-time block is a System Generator block that serves as a proxy between the simulation environment and the underlying FPGA hardware. When the design is simulated in Simulink, results for the compiled portion are calculated in hardware instead of software.

## **Co-Simulation Communication Primitives**

System Generator provides different interfaces that allow a Simulink design to communicate with an FPGA platform during hardware co-simulation. The types of interfaces that should be used depend on the particulars of the design. Each interface is briefly described below.

#### **Ports**

Ports are the most common interface for communicating with FPGA co-simulation hardware. Here the term *port* is used to include both System Generator Gateway blocks and Simulink Inport/Outport blocks. See Figure 4-1

Figure 4-1: Ports

When a design that includes a port is compiled for hardware co-simulation, a corresponding port is created in a co-simulation memory map inside the FPGA that can be written to or read from by the PC during co-simulation. A port with an equivalent name and data type is also included on the run-time co-simulation block. This means that each port in the design translates into a corresponding port on the run-time co-simulation block. In this manner, the external interface of a run-time co-simulation block is created to match the interface of the subsystem for which it was compiled. The ordering of the ports on the run-time co-simulation block follows these rules:

Simulink Inport and Outport blocks are added to a run-time co-simulation block in order of port indexes. For example, if a Simulink Inport has an index of 1, it will be the

- first input port on the co-simulation block. An Outport with an index of 2 will be the second output port on the co-simulation block.

- Because Gateway blocks lack an explicit index or ordering in Simulink, these ports are

added to a run-time co-simulation block in alphabetical order. If a design contains

both Gateways and Inport/Outport blocks, the Gateway ports appear last (i.e., they

have a higher index).

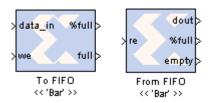

## **Shared Register**

A To Register, From Register or *shared register pair* can be generated and co-simulated in FPGA hardware. Here a shared register pair is defined as a To Register block and From Register block that specify the same name (e.g., Bar). See Figure 4-2. In hardware, a shared register is implemented using a synthesizable register component (for VHDL) or a module (for Verilog).

Figure 4-2: Shared Register Pair

When a design that includes a shared register pair is compiled for hardware co-simulation, the pair is replaced by a single register instance. Both sides of the register are attached to user design logic; that is, logic that originated from the original System Generator model. In this case, control of the register is not shared between the PC and FPGA hardware since all register ports are attached to user design logic. Compiling a shared register pair to hardware is equivalent to compiling a System Generator Register or Delay block.